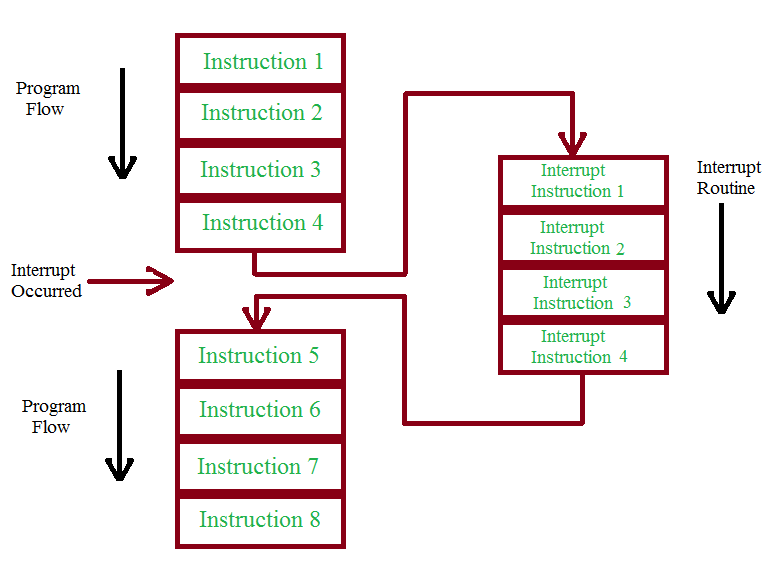

This tutorial demonstrates how to use interrupts on a processor. In this tutorial We will explain.

Nested Vector Interrup Sjsu Cmpe Embedded Courses

Connect the VICs interrupt_controller_out Avalon-ST source to the interrupt_controller_in Avalon-ST sink on either the Nios II processor or the next VIC in a daisy-chained configuration.

. Important Information for the Arm website. Modified 2 months ago. Viewed 3k times.

The Vector Table defines the entry addresses of the processor exceptions and the device specific interrupts. Modified 5 years 7 months ago. Viewed 2k times 5 2.

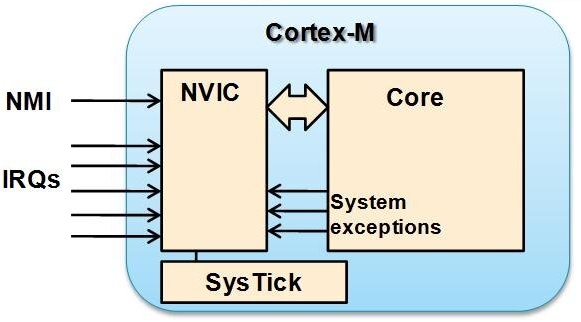

The Nested Vectored Interrupt Controller embedded inside of the STM32L4 microcontroller provides up to 91 interrupt channels on STM32L49x4A6 devices served with low latency. It supports up to 256 different interrupt vectors. The interrupt controller belongs to the Cortex-M0 CPU enabling a close coupling with the processor core.

External interrupts are maskable that is when an event occurs the peripheral will sent an interrupt request if the. Understanding the STM32 NVIC Nested Vectored Interrupt Controller The NVIC on the STM32 series of ARM Cortex-M micro-controllers is a very powerful tool that can be used to handle any type of interrupt. Each interrupt is associated with an interrupt number that is used in programming the NVIC.

Which offloads this work overhead from the CPU. All interrupts including core exceptions are managed by the NVIC core exceptions are always accepted. Which includes the Nested Vectored Interrupt Controller NVIC.

So it has 16 programmable priority levels. Because HW will become more complex if we have two interrupt. These registers are memory mapped.

There is an interrupt called each time data arrive to MCU. I saw that Cortex A9 supports a GIC. Nested Vector Interrupt Controller NVIC Objective.

If a high-priority exception interrupt is required during exception processing then the NVIC block. Nested vector interrupt control uses a vector table that contains the addresses of the ISRs for each interrupt. The Cortex-M series processors include an interrupt controller called the Nested Vector Interrupt Controller for interrupt handling such as interrupt prioritization and interrupt masking.

Ask Question Asked 6 years 11 months ago. Nested Vectored Interrupt Controller. In general you will understand the concept behind interrupts on any processor but we will use the SJ2 board as an example.

Defferent peripheral can trigger interrupt like data come to USART ADC finished conversion timer overflow and more more. Connect the VICs dummy_master Avalon Memory-Mapped. The priority for each interrupt source is programmable four levels.

I already used interrupts in my USART library. The NVIC block suspends the calculation processing that is running on the main core and controls switching to prioritized processing. Nested vector interrupt controller.

NVIC NVIC or Nested Vector Interrupt Controller is used to dinamically tell which interrupt is more important and. Differences among various interrupts. The main features are.

It is typically located at the beginning of the program memory however Using Interrupt Vector Remap it can be relocated to RAM. The interrupt architecture and priorities are very flexible and highly configurable to support RTOS. NVIC or Nested Vector Interrupt Controller is used to dinamically tell which interrupt is more important and for enabling or disabling interrupts.

Nested Vectored Interrupt Controller. Breakpoint inside interrupt C. When an interrupt is triggered the processor gets the address from the vector table.

If two pending interrupts share the same priority priority is given. Nested Vectored Interrupt Controller NVIC ARM Cortex-M Microcontrollers. Cortex-M0 Nested Vector Interrupt Controller.

Defferent peripheral can trigger interrupt like data come to USART ADC finished conversion timer overflow and more more. The NVIC contains a number of programmable registers for interrupt management such as enabledisable and priority levels. Any processorcore can support only one interrupt controller.

Ask Question Asked 5 years 7 months ago. Application could benefit from dy namic prioritization of the. 32 interrupt sources 4 programmable priority levels low-latency exception and interrupt handling Automatic nesting Power management control Applications can benefit from dynamic prioritization of the interrupt levels fast response to the.

Micro-Coded Architecture So that interrupt stacking entry and exit are done automatically in hardware. It supports the system exception and interrupt occurrence. The prioritization and handling schemes of nested vector interrupt control reduce the latency and overhead that interrupts typically introduce and ensure low power consumption.

Interrupt vector and irq mapping in do_IRQ. NVIC is an on-chip controller that provides fast and low latency response to interrupt-driven events in ARM Cortex-M MCUs. The ARM Cortex -M0 Nested Vector Interrupt Controller NVIC provides an interface between interrupt sources external to the core peripherals and external pins and the core.

One of 16 priorities could be assigned to each interrupt source. So heres a tutorial on how to use it The NVIC on the STM32F4 uses 4 bits to define priority levels. Difference between Generic Interrupt Controller and Nested Vectored Interrupt controller.

The symbol __Vectors is the address of the vector table in the startup code and the register SCB-VTOR holds the start address of the.

Nested Vectored Interrupt Controller Nvic Arm Cortex M

Nested Vectored Interrupt Controller Nvic Arm Cortex M

Blue Pill Stm32cubeide Gpio Sebagai Interupsi Blogna Kang U 2 Man

Vectored Interrupt Controller And Nested Vectored Interrupt Controller

Nested Vectored Interrupt Controller Nvic Arm Cortex M

Vectored Interrupt Controller And Nested Vectored Interrupt Controller

0 comments

Post a Comment